- 您现在的位置:买卖IC网 > Sheet目录1991 > CS4360-KZZ (Cirrus Logic Inc)IC DAC STER 6CH 102DB 28TSSOP

CS4360

DS517F2

23

4.3.2

Control Port Mode

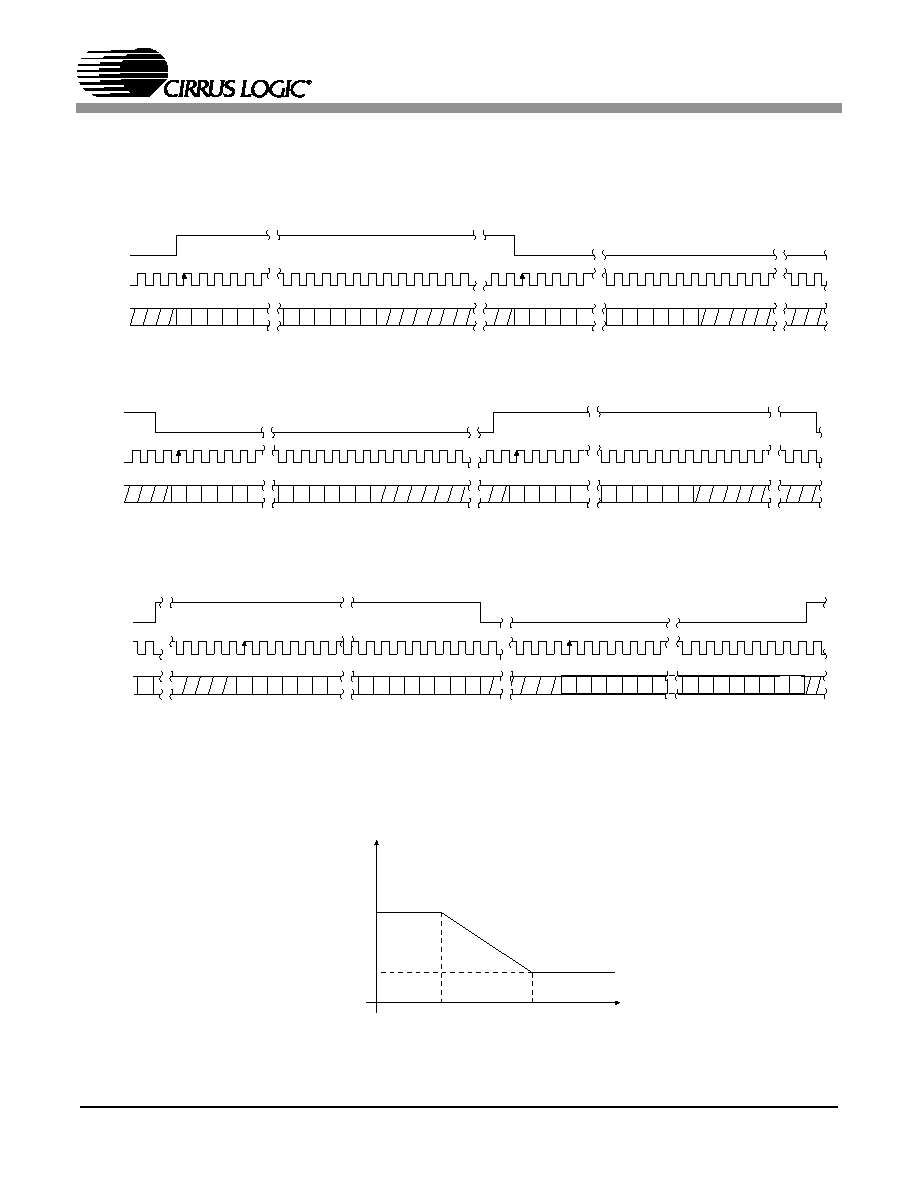

The desired format is selected via the DIF2, DIF1 and DIF0 bits in the Mode Control 2 register (see section

6.1.2). For an illustration of the required relationship between LRCK, SCLK and SDIN, see Figures 15-17.

4.4

De-Emphasis Control

The device includes on-chip digital de-emphasis. Figure 18 shows the de-emphasis curve for Fs equal to

44.1 kHz. The frequency response of the de-emphasis curve will scale proportionally with changes in

sample rate, Fs.

Notes: De-emphasis is only available in Single-speed Mode.

LR C K

SC L K

Left C hannel

R ig ht C hannel

SD IN

+3 +2 +1

+5 +4

MS B

-1 - 2 -3 -4 -5

+3 +2 +1

+5 +4

-1 -2 -3 -4

LS B

MS B

LS B

Figure 15. Left Justified up to 24-Bit Data

LR C K

SC L K

Left C hannel

R ig ht C hannel

SD IN

+3 +2 +1

+5 +4

MS B

-1 - 2 -3 -4 -5

+3 +2 +1

+5 +4

-1 -2 - 3 -4

MS B

LS B

Figure 16. I2S, up to 24-Bit Data

LRCK

SC LK

Left C hannel

SDIN

+6 +5 +4 +3

+2 +1

+7

-1 -2 -3 -4 -5

LS B

Right Cha nnel

MSB

LS B

+6 +5 +4 +3 +2 +1

+7

-1 -2 -3 -4 -5

MSB

LSB

Figure 17. Right Justified Data

Gain

dB

-10dB

0dB

Frequency

T2 = 15 s

T1=50 s

F1

F2

3.183 kHz

10.61 kHz

Figure 18. De-emphasis Curve

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CS4361-CZZR

IC DAC STER 6CH 105DB 20-TSSOP

CS4362-KQZ

IC DAC 6CH 114DB 192KHZ 48LQFP

CS4362A-DQZ

IC DAC 6CH 114DB 192KHZ 48-LQFP

CS4364-CQZR

IC DAC 103DB 24BIT 6CH 48-LQFP

CS4382A-DQZ

IC DAC 8CH 114DB 192KHZ 48-LQFP

CS4384-CQZR

IC DAC 8CH 103DB 192KHZ 48-LQFP

CS4385-DQZR

IC DAC 8CH 114DB 192KHZ 48-LQFP

CS4391A-KZZR

IC DAC 24BIT 192KHZ W/VC 20TSSOP

相关代理商/技术参数

CS4360-KZZR

功能描述:数模转换器- DAC IC 102dB 24Bit 192kHz 6ch DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS4361

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:20-Pin, 24-Bit, 192 kHz, 6-Channel D/A Converter

CS4361_08

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:20-Pin, 24-Bit, 192 kHz, 6-Channel D/A Converter

CS4361-CZZ

功能描述:音频数/模转换器 IC 6-Ch DAC 24-Bit 192kHz 105dB RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

CS4361-CZZR

功能描述:数模转换器- DAC IC 105dB 24-bit 192kHz 6ch DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS4361-DZZ

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:20-pin, 24-bit, 192 kHz, 6-channel D/A Converter

CS4362

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:114 dB, 192 kHz 6-Channel D/A Converter

CS4362_04

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:114 dB, 192 kHz 6-channel D/A Converter